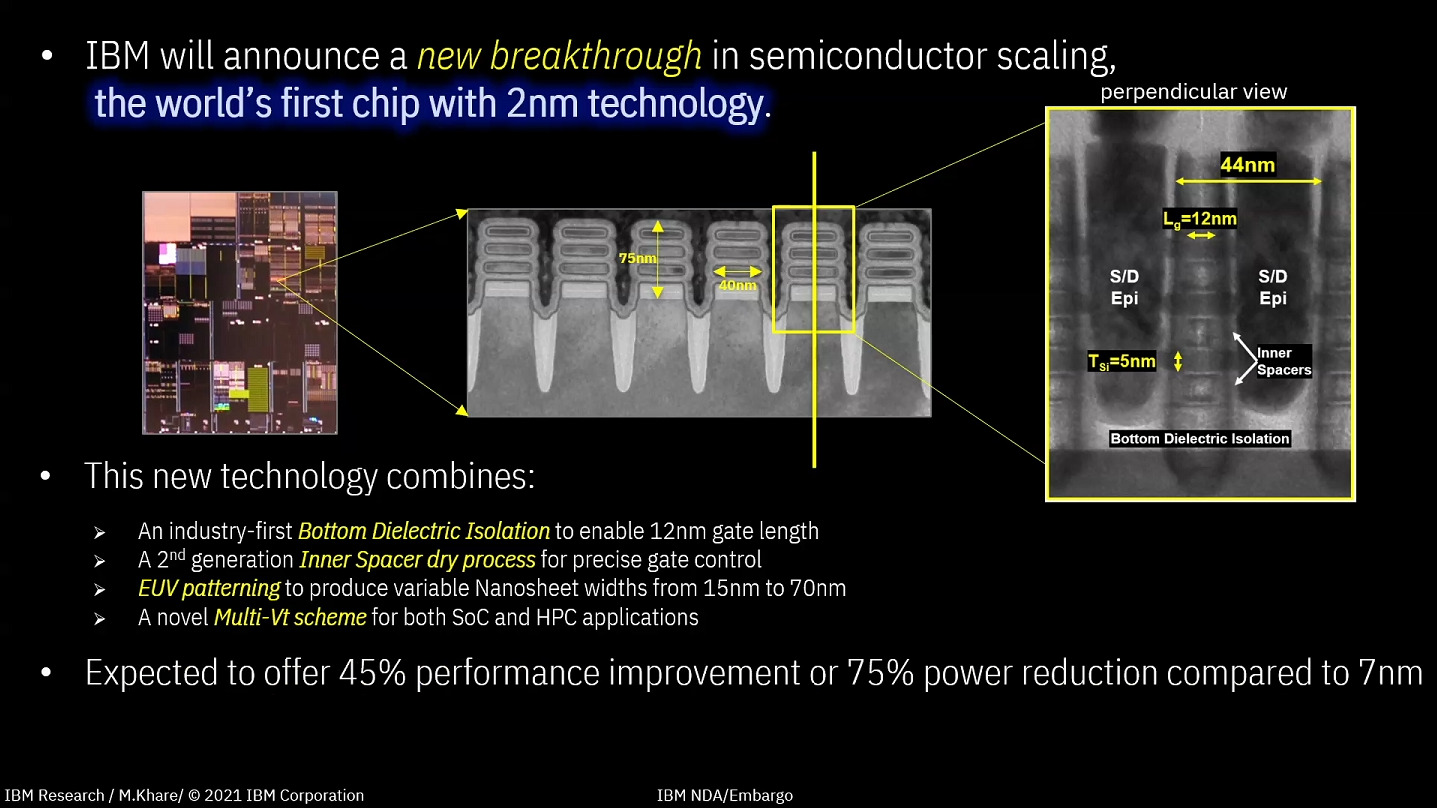

Les ingénieurs des laboratoires du groupe américain IBM ont franchi une nouvelle étape dans le développement d’architecture de puces en annonçant la première puce d’une taille de structure de 2 nanomètres.

333 millions de transistors sur un millimètre carré

2 nm… mais il faut bien entendu noter que la valeur ne correspond qu’à un équivalent. Les conceptions 3D des processus FinFET modernes suivent d’autres principes que ceux des architectures anciennes bidimensionnelles. Néanmoins, ce chiffre donne une impression de l’état de développement.

En fin de compte, il s’agit d’étendre davantage la densité des transistors sur une puce afin d’augmenter les performances, mais aussi réduire la consommation d’énergie. Par rapport à une puce de 5 nanomètres (Apple M1) ou 7 nanomètres (AMD Ryzen), cette nouvelle architecture IBM est censée apporter environ 45 % de performances en plus. Cette puissance supplémentaire est associée à 75 % d’énergie en moins.

Le tableau publié par AnandTech (qui a regroupé des données de MWikichip) permet de se rendre compte de cette fameuse densité de transistors que l’on calcule en méga-transistor par millimètre carré (MTr/mm2).

| IBM | TSMC | Intel | Samsung | |

|---|---|---|---|---|

| 22 nm | 16,5 | |||

| 16 nm / 14 nm | 28,88 | 44,67 | 33,32 | |

| 10 nm | 52,51 | 100,76 | 51,82 | |

| 7 nm | 91,2 | 237,18 | 95,08 | |

| 5 nm | 171,3 | |||

| 3 nm | 292,21 | |||

| 2 nm | 333,33 |

Comme vous pouvez le constater plus bas, IBM utilise des transistors de type « gate-allaround » (GAAFET) sur les nœuds de 2 nm. Ces transistors GAA à 3 piles d’IBM possèdent une hauteur de cellule de 75 nm, une largeur de cellule de 40 nm et chaque nanofeuille a une hauteur de 5 nm, séparées les unes des autres de 5 nm.

Cette nouvelle architecture signifie donc que 50 milliards de transistors peuvent être emballés sur une puce de la taille d’un ongle

IBM peut ainsi proposer 333 millions de transistors sur un millimètre carré. Les derniers SoC 5 nanomètres, sortis de la chaîne de production de TSMC, s’élèvent à 171 millions de transistors à titre de comparaison. Cette nouvelle architecture signifie donc que 50 milliards de transistors peuvent être emballés sur une puce de la taille d’un ongle (150 millimètres carrés).

La course à la miniaturisation

IBM est à la pointe dans le développement de semi-conducteurs. L’entreprise américaine a également été la première à présenter des puces fonctionnelles de 7 nanomètres (2015) et 5 nanomètres (2017).

L’année dernière, TSMC a surpris tout le monde lorsqu’il a annoncé que ses nœuds de 3 nm n’utiliseront pas de transistors GAAFET. Néanmoins, les nœuds de 2 nm adopteront la conception GAAFET avec une commercialisation des premières puces en 2023. Apple a ainsi conclu des accords exclusifs de production et de R&D avec TSMC jusqu’aux nœuds 2 nm. Pendant ce temps, Samsung tente de dépasser TSMC sur le 3 nm… néanmoins les nœuds de Samsung sont historiquement connus pour obtenir de moins bons rendements que ceux de TSMC.

Votre café et votre dose de tech vous attendent sur WhatsApp chaque matin avec Frandroid.

Mdrrrrr. Il faut attendre le 3nm de TSMC pour dépasser le 7nm de Intel ? Intel peut dormir tranquille 🤣🤣🤣

Ce contenu est bloqué car vous n'avez pas accepté les cookies et autres traceurs. Ce contenu est fourni par Disqus.

Pour pouvoir le visualiser, vous devez accepter l'usage étant opéré par Disqus avec vos données qui pourront être utilisées pour les finalités suivantes : vous permettre de visualiser et de partager des contenus avec des médias sociaux, favoriser le développement et l'amélioration des produits d'Humanoid et de ses partenaires, vous afficher des publicités personnalisées par rapport à votre profil et activité, vous définir un profil publicitaire personnalisé, mesurer la performance des publicités et du contenu de ce site et mesurer l'audience de ce site (en savoir plus)

En cliquant sur « J’accepte tout », vous consentez aux finalités susmentionnées pour l’ensemble des cookies et autres traceurs déposés par Humanoid et ses partenaires.

Vous gardez la possibilité de retirer votre consentement à tout moment. Pour plus d’informations, nous vous invitons à prendre connaissance de notre Politique cookies.

Gérer mes choix